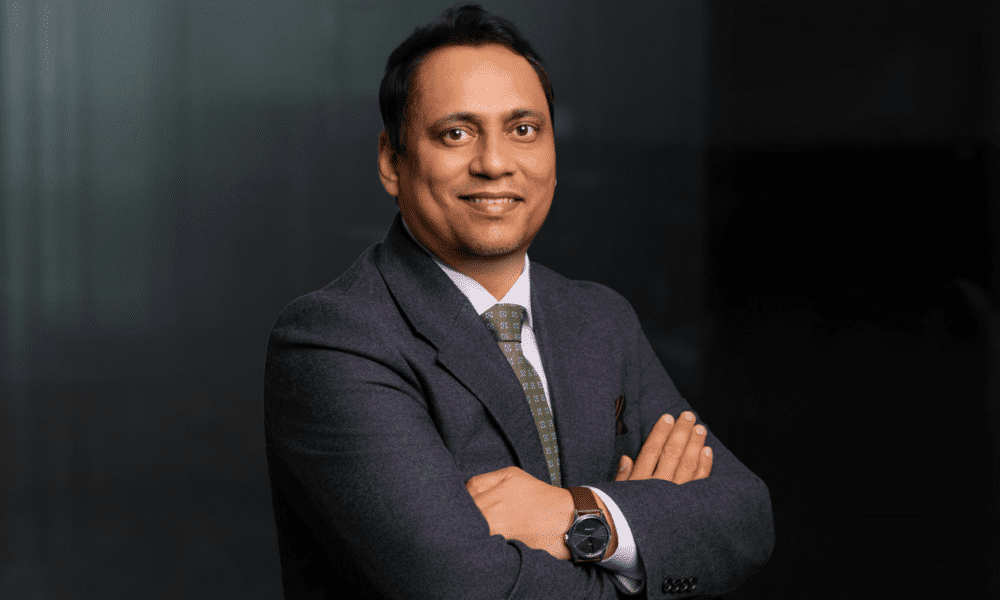

By integrating novel methodologies, the field of hardware verification is undergoing a significant transformation, addressing the complex demands of modern high-speed interface protocols. Jena Abraham, an industry expert, explores cutting-edge solutions designed to enhance efficiency and accuracy in verification processes. With a background in advanced hardware verification, Abraham provides valuable insights into innovations that are shaping the future of the field.

Redefining Verification with Hybrid Approaches

The increasing complexity of high-speed interfaces such as PCIe Gen 5/6, USB 4.0, and high-speed Ethernet has necessitated a shift from traditional verification methods to more dynamic and integrated frameworks. One of the most significant advancements is the hybrid verification methodology, which merges formal verification techniques with dynamic simulation. By combining these approaches, verification accuracy improves significantly, particularly in complex timing and error recovery scenarios.

Hybrid verification decomposes complex systems into smaller units, allowing for targeted analysis. Studies indicate that this methodology reduces verification complexity while maintaining accuracy across protocol state transitions. Additionally, the hybrid approach is instrumental in ensuring compliance with evolving interface standards and optimizing computational resource allocation, making it an indispensable tool for modern hardware verification.

Harnessing Hardware Acceleration for Speed and Efficiency

The adoption of FPGA-based verification has proven to be a game-changer for high-speed protocol testing. FPGA emulation significantly reduces the time required for verification, achieving a 60% reduction compared to conventional software simulations. Advanced FPGA architectures are designed to handle multiple protocol layers simultaneously, enabling real-time verification with precision.

Modern FPGA-based verification systems support clock frequencies of up to 250MHz, with processing latencies as low as four clock cycles for basic operations. These architectures enable cycle-accurate verification, providing a highly efficient alternative to purely software-based simulation techniques. By leveraging hardware acceleration, companies can ensure thorough and efficient verification while minimizing resource consumption. Advanced pipeline optimization and parallel processing capabilities further enhance verification throughput, enabling real-time analysis of complex system behaviors.

AI and Machine Learning: A New Era in Verification

The integration of artificial intelligence and machine learning has further optimized the verification landscape. Machine learning models, particularly those employing support vector machines and neural networks, can analyze vast amounts of test data, improving prediction accuracy and reducing verification times.

AI-driven test generation frameworks automate test creation, achieving up to 90% test coverage while reducing test case generation time by 80%. By analyzing historical data, AI models can identify patterns and automatically generate relevant test scenarios, significantly enhancing efficiency. These intelligent systems also prioritize high-impact test cases, ensuring that verification resources are allocated optimally.

Comprehensive System-Level Verification

The increasing integration of multiple high-speed protocols within a single system has introduced new verification challenges. To address this, system-level verification strategies now incorporate real-time monitoring, power-aware verification, and dynamic voltage and frequency scaling analysis.

Multi-protocol monitoring architectures enable simultaneous verification of different protocol stacks, ensuring seamless communication between interface components. Furthermore, power-aware verification techniques identify power-related issues during pre-silicon testing, optimizing energy efficiency while maintaining performance. These advancements ensure that hardware verification processes are not only accurate but also power-efficient and scalable.

The Future: Quantum Computing and Standardized Frameworks

Looking ahead, quantum computing presents promising opportunities for hardware verification. Quantum algorithms have the potential to solve traditionally intractable verification problems, significantly reducing computational complexity. Theoretical models suggest that quantum techniques could efficiently handle large-scale state space exploration, opening new avenues for verification methodologies.

Additionally, the push for standardized verification frameworks is gaining momentum. Establishing structured protocols for verification, quality control, and documentation ensures consistent and reproducible results. These frameworks provide a roadmap for future verification processes, ensuring alignment with industry standards and enhancing reliability.

In conclusion,the advancements in hardware verification methodologies are revolutionizing the field, enabling efficient and accurate testing of high-speed protocols. From hybrid verification frameworks to AI-driven test generation and FPGA-based acceleration, these innovations address the growing challenges of modern interface design. As the industry continues to evolve, the integration of quantum computing and standardized verification frameworks will further enhance efficiency and accuracy. Jena Abraham’s insights highlight the transformative impact of these advancements, paving the way for a more robust and streamlined verification process.