The rapid build-out of advanced nodes has raised the bar for how quickly and consistently design intent must translate into manufacturable silicon, from across continents to toolsets to teams. Today’s reality: getting first-time-right silicon and ramping it reliably at volume depends on rock-solid IP/logic design, fast validation feedback loops and disciplined technology transfer.

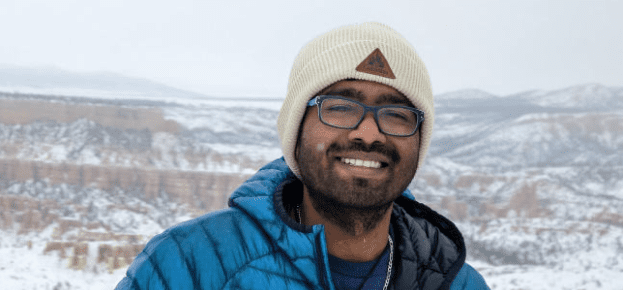

Shashikiran K. an IP/Logic Design Engineer at Intel Corporation, works at this intersection. His career spans product development, manufacturing, high-volume validation and design; what’s more, he’s known for solving complex manufacturing-flow issues and orchestrating cross-functional stakeholders worldwide. He has led technology transfers from Technology Development (TD) to Volume-Factory (VF) sites in the U.S., China and Malaysia, thereby standardizing adoption, reducing ramp risk and helping sites hit performance envelopes consistently.

Scaling Technology Transfer Across Global Fabs

Global demand signals underscore how quickly processes must be replicated and qualified across regions. The World Semiconductor Trade Statistics (WSTS) Spring 2025 outlook projects the market to grow by 11.2% in 2025 to $700.9B, extending robust momentum across logic and memory. In parallel, front-end fab equipment spending is forecast at $110B in 2025, up 2% year over year, indicating continued capital intensity for advanced lines. Finally, AI infrastructure is a powerful tailwind: Omdia expects the AI data center chip market to reach $207B in 2025 (from $123B in 2024) whose ~67% growth in a single year and forecast of $286B by 2030 amplifies pressure to stand up new capacity without yield regressions.

Within this environment, Shashikiran has led transfers from TD into VF sites in the U.S., China and Malaysia, thereby aligning design, manufacturing and validation owners so that sites behave like the golden reference from day one. He is recognized for standardizing adoption across fabs and compressing ramp risk by coordinating cross-functional handoffs and tightening control plans around known process sensitivities: contributions grounded squarely in his multi-phase lifecycle experience.

“Contrary to a ‘copy-and-paste’, a successful transfer is control. My north star is getting each site to the same behavior as the reference flow, fast and repeatably,” states Shashikiran.

Hardening the Manufacturing Flow, End-to-End

As fabs take on new technologies at speed, the challenge shifts to ensuring stability and reliability across complex manufacturing flows. Uptime and control depth decide whether promising designs become reliable, shippable parts. In semiconductor fabs, one hour of routine maintenance usually prevents 3–4 hours of unplanned downtime, which is a clear mandate for proactive reliability programs. Yield is equally unforgiving: findings estimate contamination accounts for ~75% of yield loss, spotlighting the need for contamination-aware design rules, recipes and monitoring. The stakes are industry-wide; for instance, during the 2021 shortage, automakers faced an estimated $210B in lost revenue, a vivid example of how upstream variability cascades into downstream disruption.

Against this backdrop, Shashikiran’s strength is problem-solving inside the manufacturing flow. He brings design, fab and validation teams together to isolate failure modes quickly, stabilize lines and scale proven fixes across sites. His background across development → manufacturing → high-volume validation → design helps translate learnings into tighter specs and faster bring-up while maintaining stakeholder alignment. “When issues surface on the line, speed and structure matter. Clear ownership, crisp data and disciplined fixes are how you protect yield and schedule,” notes Shashikiran.

Verification & Validation at Scale

Even as flows stabilize, the next critical hurdle is proving designs can validate against real-world factory conditions at scale. Design complexity keeps rising. Apple’s M1 Ultra alone packs 114 billion transistors, illustrating the verification burden modern Systems On Chips (SoCs) impose. Yet, in 2024, only 14% of ASIC/SoC projects achieved first-silicon success: this is the lowest rate in two decades, which means re-spins and extended validation remain common. Meanwhile, semiconductor capital expenditures are forecast at $160 billion in 2025 (a 3% rise from $155 billion in 2024), underscoring sustained investment that demands efficient verification and bring-up to earn returns.

At Intel, Shashikiran’s work spans high-volume validation and design, closing the loop between logic/IP choices and what the line can repeatedly produce. He partners tightly with validation and manufacturing so design intent, tests and fab recipes reinforce each other: this reduces ambiguity, thereby aligning expectations and accelerating stable ramps under real factory conditions. His approach shortens learning cycles, prevents yield escapes during ramp and supports consistent reliability across sites as products move from the lab to sustained high-volume production. “Great silicon is a team sport. When design, validation and fab speak the same language, yield follows,” observes Shashikiran.

Scaling Teams and Cross-Site Execution

Meeting validation and flow challenges ultimately depends on people: the engineers and teams capable of executing across geographies at speed. The workforce challenge is quantifiable; for perspective, the U.S. will need 115,000 additional semiconductor workers by 2030, with a potential shortfall of 67,000 without pipeline expansion. Globally, employers believe 44% of workers’ skills are slated for disruption in the next five-year span, keeping upskilling central to execution. In the U.S., CHIPS-enabled projects across 20 states are projected to create 125,000+ jobs, making workforce coordination as critical as equipment delivery.

Shashikiran’s communication skills and cross-functional leadership are core to his impact. He builds productive relationships with stakeholders worldwide and coordinates work across time zones and functions, ensuring knowledge transfers stick and new teams can execute confidently: this is critical as new fabs come online and existing lines absorb new processes. “Tools and recipes travel on paper, whereas capability travels through people. Clear communication is how you scale both,” states Shashikiran

Looking Ahead

Taken together, these challenges show why execution excellence, from transfer to flow and from validation to people, will decide who leads as the industry races ahead. With the semiconductor industry scaling toward $1 trillion, the combination of disciplined technology transfer, rigorous validation and seamless cross-functional execution will define who leads in the next decade. Shashikiran K.’s record at Intel demonstrates how engineering excellence translates into global manufacturing resilience: it helps ensure that the chips powering future innovation are delivered reliably, at scale. His recognition as a Globee Awards judge for innovation reflects a career built on measurable impact and high professional standards, which is exactly what advanced manufacturing needs next.

“The next wave of semiconductors is more than just smaller and faster: better still, it concerns building trust that every chip will deliver consistently at global scale. That’s the standard I aim to uphold,” says Shashikiran.